# Untersuchungen zur direkten digitalen Synthese in mobilen EIS-Anwendungen

## Zusammenfassung

Mit zunehmendem Einsatz von elektrochemischen Akkumulatoren im Fahrzeugbau entsteht die Forderung, eine zuverlässige Vorhersage über den aktuellen Ladezustand (SOC) sowie Gesundheitszustand (SOH) des Speichers treffen zu können. Bisher verwendete Standardverfahren, die häufig auf dem Prinzip der Ladungszählung beruhen, haben ihre Schwächen in der Prädiktion des SOC. Genauere Vorhersagen liefert die elektrochemische Impedanzspektroskopie (EIS), deren Anwendung aufgrund des Aufwands an Messtechnik bisher überwiegend auf Labore beschränkt war. Durch immer leistungsfähigere und effizientere Prozessoren wird dieses Verfahren zunehmend auch für den mobilen Einsatz interessant. Bei dem Verfahren werden die Akkumulatoren im Kleinsignalbereich mit sinusförmigen Spannungen beaufschlagt und durch gleichzeitige Strommessung die Impedanz bestimmt, die Rückschlüsse auf den SOC zulassen. Ein wesentlicher Baustein des Verfahrens ist die Erzeugung möglichst idealer Sinusspannungen variabler Frequenz, die mit Prozessoren und dem Verfahren der direkten digitalen Synthese (DDS) realisiert werden. Dadurch sinkt der anschließende Aufwand zur Filterung erheblich. In diesem Beitrag werden daher zwei DDS-Verfahren untersucht und hinsichtlich der Erzeugung möglichst idealer Sinusfunktionen zum Einsatz in mobilen EIS-Anwendungen verglichen.

#### **Abstract**

With the increasing use of electrochemical accumulators in vehicle construction, there is a need to be able to reliably predict the current state of charge (SOC) and state of health (SOH) of the storage device. Up until now, used standard methods, which are often based on the principle of charge counting, have their weaknesses in predicting the SOC. More accurate predictions are provided by electrochemical impedance spectroscopy (EIS). This method has so far mainly been limited to laboratories due to the complexity of the measurement technology. Due to ever more powerful and efficient processors, this method is also becoming increasingly interesting for mobile applications. With this method the accumulators are subjected to sinusoidal voltages in a smallsignal range and the impedance is determined by simultaneously measuring the current, which allows predictions about the SOC. An essential component of the process is the generation of nearly ideal sinusoidal voltages of variable frequency, which are realized with processors and the direct digital synthesis (DDS). This would significantly reduce subsequent filter efforts. Therefore, in this article, two DDS methods are examined and compared with respect to the generation of the most ideal possible sine functions for use in mobile EIS applications.

# 1 Einleitung

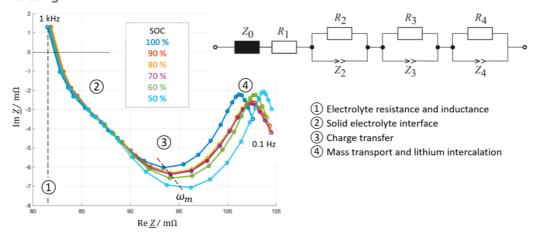

Abbildung 1: Nyquist-Diagramm der Impedanz einer Lithiumionenbatterie für verschiedene Ladezustände (links) sowie ein elektrisches Ersatzschaltbild (rechts)

Mit zunehmender Elektrifizierung heutiger Kraftfahrzeuge nimmt auch die Bedeutung der Überwachung und Voraussage des Ladezustands (SOC) mobiler elektrochemischer Energiespeicher zu, um eine zuverlässige Aussage über die restliche Reichweite bis zum nächsten Ladevorgang treffen zu können. Eine möglicherweise genauere Vorhersage als bisher verwendete Methoden liefert das Verfahren der elektrochemischen Impedanzspektroskopie (EIS). Dieses beaufschlagt für einen definierten Frequenzbereich den Energiespeicher mit diskreten sinusförmigen Spannungen im Kleinsignalbereich und berechnet aus den sinusförmigen Systemantworten eine frequenzabhängige Impedanz  $\underline{Z}$  nach Abbildung 1 [1-2]:

$$\underline{Z} = \frac{\underline{U}_{\text{eff}}}{\underline{I}_{\text{eff}}} = Z \cdot e^{j\omega t}$$

Deren Imaginärteil wiederum lässt direkte Rückschlüsse auf den Ladezustand der Batterie zu [2]. Das bevorzugt im Laborbereich verwendete Verfahren kann durch immer leistungsfähigere mobile Prozessoren in Form von Mikrocontrollern inzwischen auch in nichtstationären Bereichen verwendet werden. Eine Aufgabe ist dabei die möglichst ideale Erzeugung sinusförmiger Spannungen unter Verwendung der im Mikrocontroller integrierter Hardware, um den anschließenden Filteraufwand möglichst gering und den Bauraum klein zu halten.

Daher wurden für einen für EIS-Anwendungen interessanten Frequenzbereich der Grundfrequenz von  $1~{\rm Hz} \le f \le 10~{\rm kHz}$  zwei Verfahren zur Erzeugung sinusförmiger Ausgangsspannungen miteinander verglichen. Bei beiden Verfahren handelt es sich um eine direkte digitale Synthese (DDS) der Ausgangsspannungen. Dabei werden die im Grunde beliebig vorgebbaren periodischen Ausgangsspannungsverläufe in prozessorinternen Speichertabellen abgelegt und in zyklischen Zeitintervallen an die ebenfalls prozessorinterne Hardware zur Ausgabe weitergereicht. Im Detail unterscheiden sich beide Verfahren darin, ob jeder hinterlegte Wert der Speichertabelle ausgegeben wird, oder ob Teilbereiche durch Unterabtastung ausgelassen werden.

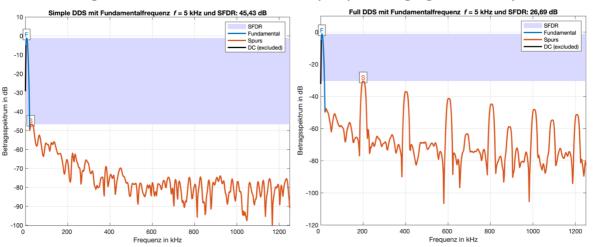

Nach Realisierung beider Verfahren und Durchführung der Messungen wurden die Ergebnisse unter Verwendung des SFDR-Wertes beurteilt. Dieser Wert in dB kennzeichnet den Abstand der größten Störung zur Grundschwingung in einem Spektrum. Große Werte kennzeichnen gute Annäherungen an ideale Sinusverläufe, kleinere Werte schlechtere.

# 2 Direkte Digitale Synthese

# 2.1. Einfache Direkte Digitale Synthese - SDDS

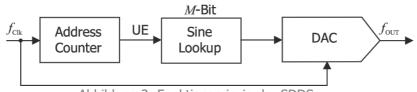

Bei der einfachen direkten digitalen Synthese (SDDS) nach Abbildung 2 wird im einfachsten Fall eine ganze Periode der auszugebenden Funktion in einer Lookup-Tabelle mit M Werten im Speicher hinterlegt [3].

Abbildung 2: Funktionsprinzip der SDDS

Ein Zähler mit der Zählfrequenz  $f_{\rm Clk}$  erzeugt bei Erreichen eines vorgebbaren Zählwertes ARR ein Triggersignal UE an die CPU oder einen DMA Controller, um den aktuellen Tabellenwert an das Ausgaberegister eines DAC zu übertragen. Die Frequenz der so ausgegebenen Sinusfunktion berechnet sich zu:

$$f_{\text{OUT}} = \frac{f_{\text{Clk}}}{M \cdot (\text{ARR} + 1)}$$

Bei den Untersuchungen war  $f_{\rm Clk}=80~{\rm MHz}$  und M=500, die verschiedenen Frequenzen wurden durch Veränderung des ARR realisiert. Für eine Ausgangsfrequenz  $f_{\rm OUT}=1~{\rm Hz}$  ist beispielsweise ARR = 159999, für  $f_{\rm OUT}=10~{\rm kHz}$  ergibt sich ARR = 15. Für noch höhere Ausgangsfrequenzen wäre dieses Verfahren ungeeignet, diese werden jedoch bei EIS-Anwendungen nicht benötigt. Der große Vorteil ist, dass bei der SDDS und Verwendung eines DMA Controllers die CPU keine Rechenleistung zur Verfügung stellen muss.

### 2.2. Vollständige Direkte Digitale Synthese - FDDS

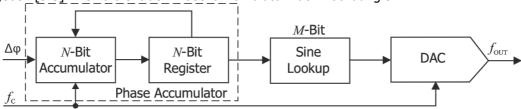

Bei der vollständigen direkten digitalen Synthese (FDDS) wird in Abhängigkeit von der zu realisierenden Ausgangsfrequenz durch Unterabtastung nur eine Teilmenge der Tabellenwerte ausgegeben [3-5]. Hierzu dient der Phasenakkumulator nach Abbildung 3.

Abbildung 3: Funktionsprinzip der FDDS

Die Ausgangsfrequenz berechnet sich mit dieser Methode zu:

$$f_{\text{OUT}} = f_{\text{C}} \cdot \frac{\Delta \varphi}{2^N} = \frac{f_{\text{Clk}}}{2^N \cdot (\text{ARR} + 1)} \cdot \Delta \varphi$$

Mit dem Phaseninkrement  $\Delta \varphi$  lässt sich die Ausgangsfrequenz bei unverändertem ARR variieren. Bei dem verwendeten N=32 Bit Zähler mit  $f_{\rm Clk}=80$  MHz und konstantem ARR = 399 folgt für eine gewünschte Ausgangsfrequenz  $f_{\rm OUT}=10$  kHz zum Beispiel ein Phaseninkrement von  $\Delta \varphi=214.748.365$ . Bei einer Sinustabelle mit 512 Einträgen werden nur die oberen  $M=\log_2(512)=9$  Bit des 32 Bit breiten Akkumulatorausgangs  $\varphi:=\varphi+\Delta\varphi$  verwendet, um den auszugebenden Tabellenwert zu bestimmen. Mit einer Verringerung von ARR wäre dieses Verfahren auch für deutlich höhere Ausgangsfrequenzen geeignet. Bei Anwendung in der EIS hat es jedoch den Nachteil einer verminderten Signalqualität des Ausgangssignals aufgrund der Unterabtastung der Tabellenwerte, wie im Folgenden gezeigt wird.

#### 3 Messungen

#### 3.1. Messmittel

Für die Untersuchungen von SDDS und FDDS wurden C-Programme erstellt und diese auf einer Testhardware [6-7] der Firma STMicroelectronics ausgeführt. Die resultierenden Ausgaben des internen 12-Bit-DAC wurden mit einem Digitaloszilloskop [8] mit einer maximalen Abtastrate von  $f_{\rm max}=2.5$  GSa/s aufgezeichnet und anschließend mit dem Programmpaket Matlab [9-10] ausgewertet.

Bei der Aufzeichnung wurde ein Modus eingestellt [11], der zu einer Erhöhung der vertikalen Auflösung n sowie zur Reduktion der Bandbreite b und somit zur Vergrößerung des SNR der Messung führt:

$$n = 8 + \frac{1}{2} \log_2 \frac{f_S}{f_{max}}$$

und  $b = 0.44 \cdot f_S$

#### 3.2. Auswertungen

Die Abtastfrequenzen  $f_{S_t}$  Auflösungen n sowie Bandbreiten b des Oszilloskops sind für die gemessenen Grundfrequenzen f der Tabelle 1 zu entnehmen.

| f/Hz            | 1    | 2    | 5    | 10   | 20   | 50   | 100  | 200  | 500   | 1000  | 2000  | 5000   | 10000  |

|-----------------|------|------|------|------|------|------|------|------|-------|-------|-------|--------|--------|

| $f_{S}/(kSa/s)$ | 0,5  | 1    | 2,5  | 5    | 10   | 25   | 50   | 100  | 250   | 500   | 1000  | 2500   | 5000   |

| n/Bit           | 19,1 | 18,6 | 18,0 | 17,5 | 17,0 | 16,3 | 15,8 | 15,3 | 14,6  | 14,1  | 13,6  | 13,0   | 12,5   |

| b/kHz           | 0,2  | 0,4  | 1,1  | 2,2  | 4,4  | 11,0 | 22,0 | 44,0 | 110,0 | 220,0 | 440,0 | 1100,0 | 2200,0 |

Tabelle 1: Abtastfrequenz, Auflösung und Bandbreite in Abhängigkeit gemessener Grundfrequenzen

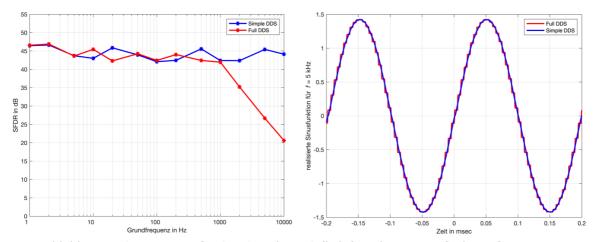

Abbildung 4: SFDR-Werte für SDDS und FDDS (links) und Ausgangsfunktion für f = 5 kHz

Abbildung 5: Spektrum für SDDS- (links) und FDDS-Verfahren (rechts) für f = 5 kHz Grundfrequenz

Die Auswertungen ergaben, dass nach Abbildung 4 (links) für Grundfrequenzen bis  $f=1~\mathrm{kHz}$  sowohl das SDDS- als auch das FDDS-Verfahren etwa gleichwertige SFDR-Werte liefern. Für höhere Grundfrequenzen  $f>1~\mathrm{kHz}$  fallen für das FDDS-Verfahren die SFDR-Werte im Vergleich zum SDDS-Verfahren stark ab. Die durch die Unterabtastung auftretenden höherfrequenten Anteile sind beispielhaft für  $f=5~\mathrm{kHz}$  Grundfrequenz sowohl im Zeitverlauf nach Abbildung 4 (rechts), als auch im Spektrum nach Abbildung 5 (rechts) deutlich sichtbar. Für das SDDS-Verfahren gemäß Abbildung 5 (links) verändert sich das Spektrum auch für  $f=5~\mathrm{kHz}$  Grundfrequenz nur unwesentlich.

# 4 Ergebnisse

Für einen Frequenzbereich bis etwa 1 kHz Grundfrequenz sind zur Realisierung mobiler EIS-Verfahren mit Mikrocontrollern sowohl das SDDS- als auch das FDDS-Verfahren zur Erzeugung sinusförmiger Anregungen gut geeignet. Das SDDS-Verfahren lässt sich bei Verwendung von Mikrocontrollern mit eingebautem DMA-Controller jedoch einfacher realisieren und bietet zudem den Vorteil, dass die CPU deutlich entlastet wird. Dadurch steht mehr Rechenleistung für andere Aufgaben zu Verfügung.

Sollen Grundfrequenzen oberhalb von 1 kHz bis etwa 10 kHz realisiert werden, sollte aufgrund der deutlich geringeren harmonischen Anteile das SDDS-Verfahren verwendet werden. Erst für noch höhere Frequenzen oberhalb von 10 kHz, die für EIS-Anwendungen jedoch uninteressant sind, ist die Verwendung des FDDS-Verfahrens unvermeidlich, verbunden jedoch mit einem entsprechend höheren Filterungsaufwand der Ausgangsspannung.

#### 5 Referenzen

- [1] B. Frenzel, P. Kurzweil, F. Gebhard, "Elektrotechnik," in *Physik Formelsammlung*, 5. Auflage, Wiesbaden, Springer Vieweg, 2021, pp. 253-254

- [2] P. Kurzweil, W. Scheuerpflug, B. Frenzel, C. Schell, and J. Schottenbauer, "Differential Capacity as a Tool for SOC and SOH Estimation of Lithium Ion Batteries Using Charge/Discharge Curves, Cyclic Voltammetry, Impedance Spectroscopy, and Heat Events: A Tutorial," *Energies*, vol. 15, no. 13, p. 4520, Jun. 2022, doi: 10.3390/en15134520. [Online]. Verfügbar: http://dx.doi.org/10.3390/en15134520

- [3] Analog Devices (1999). *A Technical Tutorial on Digital Signal Synthesis*. [Online]. Verfügbar: https://www.analog.com/en/education/education-library/technical-tutorial-dds.html

- [4] E. Murphy, C. Slattery (2004). *All About Direct Digital Synthesis*. [Online]. Verfügbar: https://www.analog.com/en/analog-dialogue/articles/all-about-direct-digital-synthesis.html

- [5] P.-T. Chen, F.-Y. Zeng, X.-H. Zhang, R.-J. Chung, C.-J. Yang, and K. D. Huang, "Composite Sinusoidal Waveform Generated by Direct Digital Synthesis for Healthy Charging of Lithium-Ion Batteries," *Energies*, vol. 13, no. 4, p. 814, Feb. 2020, doi: 10.3390/en13040814. [Online]. Verfügbar: http://dx.doi.org/10.3390/en13040814

- [6] STMicroelectronics (2020). *UM1724 User Manual, STM32 Nucleo-64 boards (MB1136)*. [Online]. Verfügbar: https://www.st.com/resource/en/user\_manual/um1724-stm32-nucleo64-boards-mb1136-stmicroelectronics.pdf

- [7] STMicroelectronics (2022). STM32 Nucleo-64 development board with STM32L476RG MCU. [Online]. Verfügbar: https://www.st.com/en/evaluation-tools/nucleo-l476rg.html

- [8] Tektronix (2004). Serien MSO3000 und DPO3000 Digital-Phosphor-Oszilloskope, Benutzerhandbuch. [Online]. Verfügbar: https://download.tek.com/manual/071265902web\_0.pdf

- [9] Mathworks (2022). Matlab. [Online]. Verfügbar: https://de.mathworks.com/help/matlab/

- [10] Mathworks (2022). Signal Processing Toolbox. [Online]. Verfügbar: https://de.mathworks.com/help/signal/

- [11] Tektronix (2013). *Tools to Boost Oscilloscope Measurement Resolution to More than 11 Bits, Application Note.* [Online]. Verfügbar: https://download.tek.com/document/48W\_27802\_2\_Letter.pdf

#### Kontakt:

Prof. Dr.-Ing. Bernhard Frenzel

Ostbayerische Technische

Hochschule (OTH) Amberg-Weiden

Fakultät Maschinenbau/Umwelttechnik

Labor für Mechatronik

und Regelungstechnik

Kaiser-Wilhelm-Ring 23

92224 Amberg

h.frenzel@oth-aw.de

Prof. Dr. Peter Kurzweil

Ostbayerische Technische

Hochschule (OTH) Amberg-Weiden

Fakultät Maschinenbau/Umwelttechnik

Labor für Elektrochemie

und Umweltanalytik

Kaiser-Wilhelm-Ring 23

92224 Amberg

p.kurzweil@oth-aw.de